|

Vhdl program for 2 1 mux2019-11-26 10:58I need to program a multiplexer and a testbench for it. Multiplexer needs to be 4to1 using 3 times 2to1 multiplexers Scheme picture. 4to1 multiplexer inputs need to be 5bit long and selecters 1 bit long.Preventing Latch Inference Ifstatements and case statements must be completely specified or VHDL compiler infers latches. A default assignment must be made so that vhdl program for 2 1 muxMar 07, 2010 Here is the code for 4: 1 MUX using case statements. The module contains 4 single bit input lines and one 2 bit select input. The output is a single bit line. Library IEEE; programme vhdl d'un multiplexeur 41 en utilisant 2 demi multiplexeurs.

Reply Delete.Jun 26, 2016 Six different Verilog methods for creating a 2 to 1 mux: gate primitives, bitwise operators, continuous assignment, case statement, if else statement, and ternary operator. VHDL, VHDL Programs A 2to1 multiplexer consists of two inputs, one select input and one output. Depends on the select signal, the output is connected to either of the inputs. Vhdl program for 2 1 mux VHDL for FPGA DesignMultiplexer.

From Wikibooks, open books for an open world VHDL for FPGA Design. 1 Multiplexer VHDL Code; 2 Multiplexer Testbench Code; 3 Multiplexer Simulation Waveform; 4 Video Links; Multiplexer VHDL Code.

Oct 14, 2015 The table above provides detailed information about the Beautiful Star of Bethlehem alto.mid file. The waveform image is automatically generated after the midi file has been converted by analyzing the resulting mp3 file. Print and download in PDF or MIDI O Beautiful Star of Bethlehem - R. Fischer Boyce. Free sheet music for Piano. Made by tmsalomon. Beautiful star of bethlehem hymn. Authoritative information about the hymn text Beautiful star of Bethlehem, shine, with lyrics, MIDI files, printable scores, PDF files, and audio recordings. Oct 14, 2015 The table above provides detailed information about the Beautiful Star of Bethlehem soprano.mid file. The waveform image is automatically generated after the midi file has been converted by analyzing the resulting mp3 file.

Mixvibes u-mix control pro manual. Library IEEE; use IEEE. STDLOGIC1164.Jan 10, 2018 VHDL 4 to 1 Mux (Multiplexer) January 10, 2018 January 29, 2016 by shahul akthar.

Multiplexer (MUX) select one input from the multiple inputs and forwarded to output line through selection line. It consist of 2 power n input and 1 output. The vhdl program for 2 1 mux What is VHDL program for 8 to 1 multiplexer? Already exists.

Purdue University's College of Technology in Indiana currently offers a 2 year bachelor's degree program as well. Dec 24, 2012 FourBit Wide 2 to 1 Multiplexer.

The 2 to 1 multiplexer is shown below. A logic 1 on the SEL line will connect the 4bit input bus A to the 4bit output bus X. A logic 0 on the SEL line will connect input bus B to output bus X. 4bit 2 to 1 Multiplexer. The VHDL code for implementing the 4bit 2 to 1 multiplexer is shown here. Write a vhdl program for 8 to 1 multiplexer Multiplexer is a digital switch. It allows digital information from several sources to be rooted on to a single output line.

The basic multi How to increase platelet count during Dengue fever A VHDL program for 64 to 1 multiplexer using four 4 to 1multiplexers is not possible, as four 4 to 1 multiplexers provideonly 16 inputs, only 14 of what is needed. Share with friends. Rating: 4.51 / Views: 808.

Vhdl Program For 2 Bit Alu Design

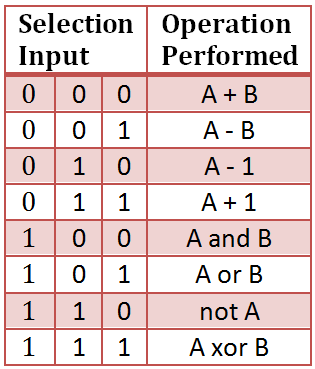

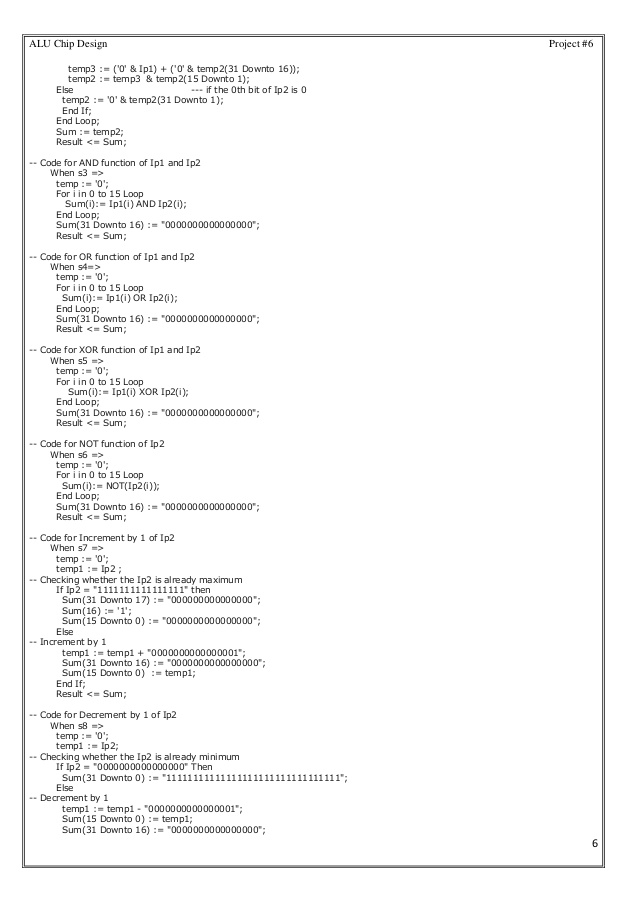

Hello my friends its me Drifter programming! Today we get back to VHDL starting off a small Series. I will start writing Components/Hardware of Computers starting off with an Simple ALU (Arithmetic Logic Unit) that we will Code in 3 parts. Today I will get into the basic Layout of the ALU that we will make talking about the Operations that it will handle and we will also write the Adder/Subber Components! So, without further do let's get started!ALU Layout/Operations:A ALU is a part/unit of a CPU that handles the Arithmetic and Boolean Operations.

We will create a 16-bit ALU that will get two 8-bit inputs (a and b) and returns a 16-bit result. C program graphics.h pdf. The selection code will be a 4-bit binary number. I will write the ALU in structural VHDL, writing most Operations as separate Circuits!The Operations that the ALU will perform are:. ADD - a + b. SUB1 - a - b.

SUB2 - b - a. INCRA - a.

INCRB - b. DECRA - a-. DECRB - b-.

MUL - a. b. NOTA - a'. NOTB - b'. AND - a and b. OR - a or b.

XOR - a xor b. COMP - a equals b a less than b a greater then bWe will get into how we will implement it using with-select in the last part (part 3).Let's now write the Add, Sub, Incr and Decr Components/Circuits! Adder Component:If you remember from we said that an N-bit Adder is made up of 1 Half Adder and N-1 Full Adders. That's exactly how we will write him! We will also use Basic Gates to implement the Half and Full Adders in the same way I showed you in Theory. For the Half Adder we will be using a AND and XOR Gate and for the Full Adder, two Half Adders and one OR Gate! For sake of simplicity I will implement the Half Adder in dataflow and the Full Adder in structural VHDL.

Vhdl Code For 1 Bit Alu

I will also don't write the simple Circuits and suppose we wrote them!So, the Half Adder looks like this: library ieee; use ieee.stdlogic1164.all; entity halfadder is port( a, b: in stdlogic; s, c: out stdlogic ); end halfadder; architecture arch of halfadder is begin s.

Comments are closed.

|

RSS Feed

RSS Feed